本研究は独立行政法人新エネルギー・産業技術総合研究所における研究テーマとして、平成23年度より開始したものです。

現在、株式会社 東芝、ルネサスエレクトロニクス株式会社、ローム株式会社と共同で実施しています。

本研究は独立行政法人新エネルギー・産業技術総合研究所における研究テーマとして、平成23年度より開始したものです。

現在、株式会社 東芝、ルネサスエレクトロニクス株式会社、ローム株式会社と共同で実施しています。

コンピュータシステムにおいて消費される電力は、演算・制御動作に伴って消費されるダイナミック電力と、待機時にも消費されるスタティック電力に大別されます。 このうちスタティック電力は実際の仕事に貢献しない電力であることからこの部分の消費電力を削減することが、システムの消費電力を最小化させるために必要不可欠です。 現在の社会環境においては、高性能演算処理に限らず生活のあらゆる場面で大小様々なコンピュータが利用されており、その中には動作時間よりも待機時間が遙かに長いものも少なくありません。 例えば、生体・環境測定においては数秒〜数分の測定間隔で動作しており、さらに1回の測定に必要な処理時間は数ミリ秒程度です。つまり、実際の動作時間の割合は非常に少なく、ほとんどが待機時間です。 本研究プロジェクトでは、真に動作すべき構成要素以外の電源を積極的に遮断する「ノーマリーオフ」を徹底的に実現し、格段の低消費電力化を図るコンピューティング手法の確立を目指します。

スタティック電力を削減する手法としては、パワーゲーティング(Power Gating:電源遮断)が有望な手法ですが、従来のコンピュータシステムに適用すると、システム内部の一時記憶が失われてしまうため、その利用範囲は限られていました。しかし近年急速に研究開発が進んでいる不揮発メモリを使えば、電源遮断時にも情報を保持できるため、パワーゲーティングによる低電力効果を最大限に活用することが出来ます。

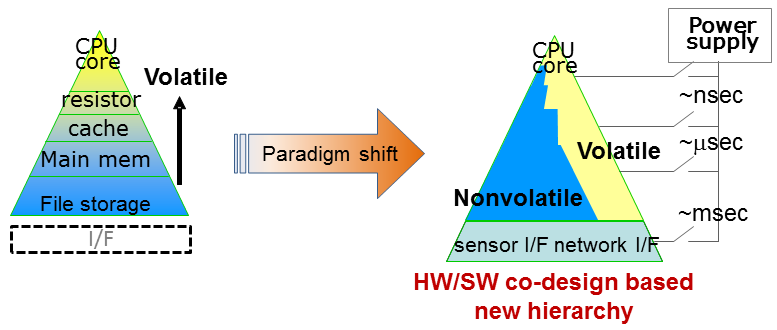

不揮発性メモリには、大容量化には向くがアクセス時の速度は遅い、間歇動作の時間間隔が長いほど低電力効果を発揮できる、という特徴があります。そこで、上記目標を達成するために、新しいメモリ階層の設計、および間歇動作を指向する新しいコンピューティング手法の2つの技術開発を、アルゴリズム〜基本ソフトウェア〜アーキテクチャの多岐にわたるシステム階層間の協調最適化により実施します。

図1: 新しいメモリ階層の設計

本研究の目的は、メモリ階層を含めたシステム全体の再設計により、待機時電力のような不必要な電力を極限まで低減させることです。その戦略として、不揮発メモリのような最先端のテクノロジーを用いたアプローチを採用しています。