本研究は半導体理工学研究センターにおける「大学との共同研究」の研究テーマとして、平成22年度より開始したものです。

本研究は半導体理工学研究センターにおける「大学との共同研究」の研究テーマとして、平成22年度より開始したものです。

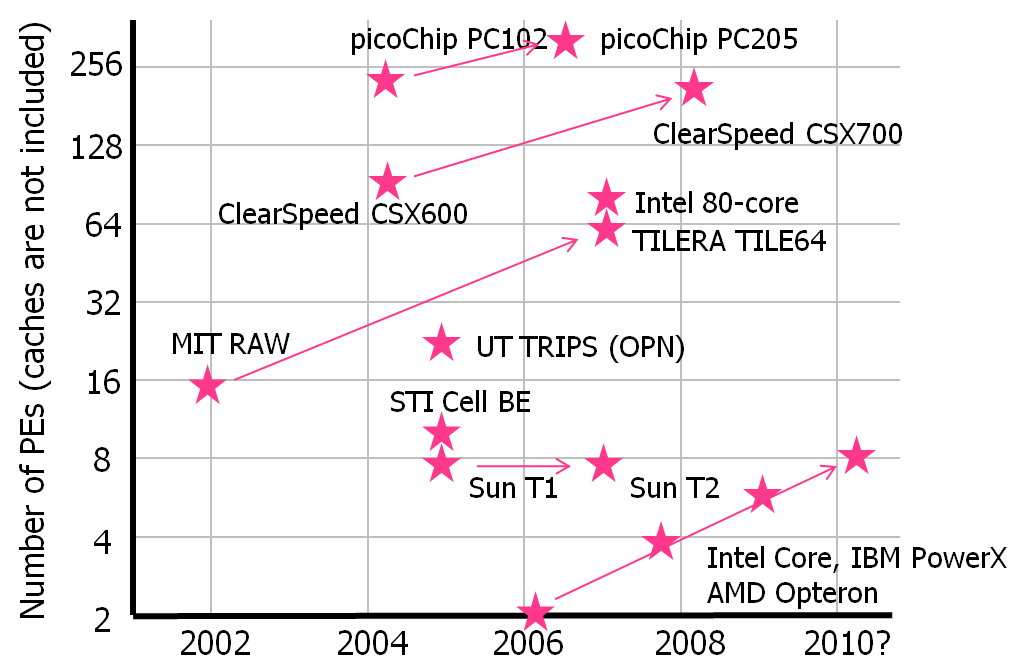

半導体プロセスの微細化によりチップ内に複数のプロセッサコアを搭載するマルチコアプロセッサが広く普及しており、今後はさらに多数のコアを搭載するメニーコアプロセッサが主流になると予想されています。また、メモリや専用回路などを搭載する System-on-Chip (SoC)も多数のコアを持つメニーコアアーキテクチャが採用されると予想されています。しかし、このようにチップ上に多くのコアが搭載されるようになると、チップ上のデータ通信路のバンド幅不足やレーテンシ増大が全体の性能・消費電力に及ぼす悪影響は深刻になってきます。そこで、多階層のバスではなく、ルータを利用したパケットスイッチングにより各IPを結合するNetwork-on-Chip (NoC)を用いたSoC設計が近年注目されるようになってきています。しかし、NoC型メニーコアSoCの実現には、 設計空間が膨大なことによる設計最適化の困難さと、NoCの特性を考慮したSoC全体のアーキテクチャ最適化が不十分さ、という2つの大きな問題があります。

図1: 近年のマルチコアプロセッサの動向

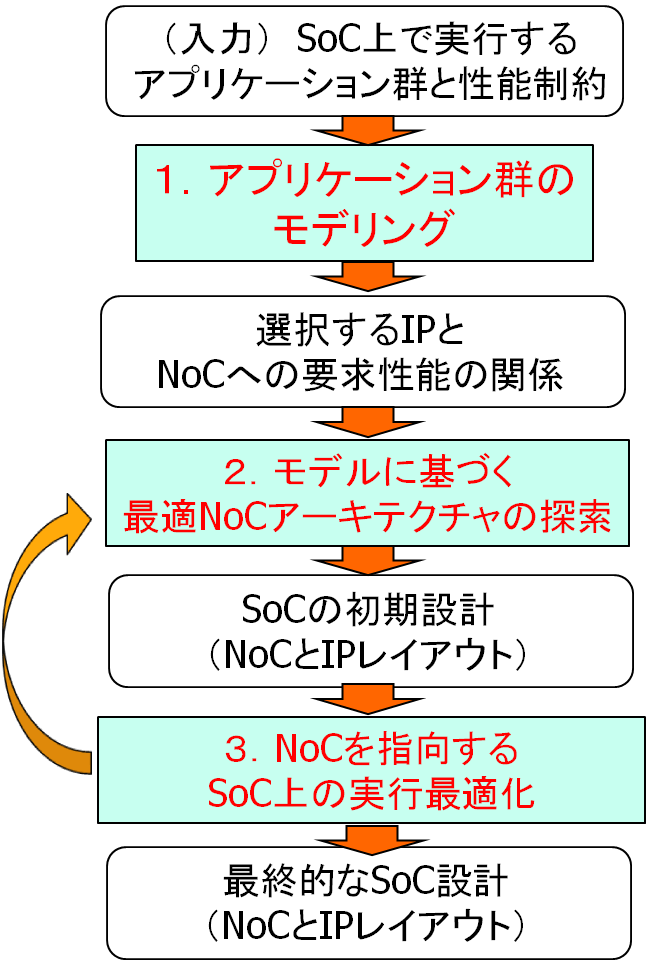

本研究の目的は、これらの問題を解決し、半導体集積度の向上の恩恵を真に享受できるNoC型メニーコアSoCを実現することです。その戦略として、チップ内データ通信が性能、電力、実装コストいずれの面でもSoC実現上の大きな制約となるという観点に立ち「NoC指向設計」というオリジナルなアプローチを採用しています。

図2: 設計フロー